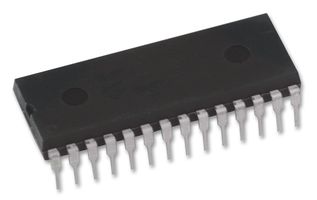

PIC24FJ64GA002-I/SP,1332298,微控制器, 16位, AEC-Q100, PIC24FJ, 32 MHz, 64 KB, 8 KB, 28 引脚, DIP,MICROCHIP

AUGAT - TE CONNECTIVITY

芯片和元件插座, 800系列, DIP插座, 28 触点, 2.54 mm, 15.24 mm, 镀金触芯

MICROCHIP

开发板, PIC24FJ128GA010 + DSPIC33FJ256GP710微控制器插入模块, Explorer 16, 16x2液晶屏

进行最后一道重要生产流程所在的国家